# **Verilog-to-Routing Documentation**

Release 8.1.0-dev

**VTR Developers**

Jun 09, 2020

# QUICK START

| 1 | VTR            | Quick Start                                  | 3 |

|---|----------------|----------------------------------------------|---|

|   | 1.1            | Setting Up VTR                               | 3 |

|   | 1.2            | Running VPR                                  | 4 |

|   | 1.3            | Running the VTR Flow                         | 8 |

|   | 1.4            | Next Steps                                   | 5 |

| 2 | VTR            | 1                                            | 0 |

| 4 | <b>VIK</b> 2.1 | VTR CAD Flow                                 |   |

|   | 2.1            | Get VTR                                      |   |

|   | 2.2            | Install VTR                                  |   |

|   | 2.3            | Running the VTR Flow                         |   |

|   | 2.4            | Benchmarks                                   |   |

|   | 2.5            | Power Estimation                             |   |

|   | 2.0            | Tasks         3                              |   |

|   | 2.7            | run_vtr_flow                                 | - |

|   | 2.8<br>2.9     | run_vtr_task                                 |   |

|   | 2.9            | parse_vtr_flow                               |   |

|   | 2.10           | parse_vtr_task                               |   |

|   | 2.11           |                                              | - |

|   |                | 8                                            | - |

|   | 2.13           | Pass Requirements                            | U |

| 3 | FPG            | A Architecture Description 5.                | 3 |

|   | 3.1            | Architecture Reference                       | 3 |

|   | 3.2            | Example Architecture Specification           | 5 |

| 4 | VPR            | 12                                           | 7 |

| 4 | <b>4</b> .1    | Basic flow                                   |   |

|   | 4.1            | Command-line Options                         |   |

|   | 4.2<br>4.3     | Graphics                                     |   |

|   | 4.5            | Timing Constraints                           |   |

|   | 4.4<br>4.5     | SDC Commands                                 |   |

|   | 4.5            |                                              |   |

|   | 4.0<br>4.7     | File Formats    16      Debugging Aids    18 |   |

|   | 4.7            |                                              | 9 |

| 5 | Odin           | II 19                                        | 1 |

|   | 5.1            | INSTALL                                      | 1 |

|   | 5.2            | USAGE                                        | 2 |

|   | 5.3            | DOCUMENTING ODIN II                          | 7 |

|   | 5.4            | TESTING ODIN II         19                   | 7 |

|   | 5.5            | USING MODELSIM TO TEST ODIN II               |   |

|     | 5.6                                      | CONTACT                                                                                                          | 198                      |

|-----|------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------|

| 6   | ABC                                      |                                                                                                                  | 199                      |

| 7   | <b>Tutor</b><br>7.1<br>7.2<br>7.3<br>7.4 | tialsDesign Flow TutorialsArchitecture ModelingRunning the Titan BenchmarksPost-Implementation Timing Simulation | 202<br>256               |

| 8   | <b>Utilit</b><br>8.1<br>8.2              | ies<br>FPGA Assembly (FASM) Output Support                                                                       |                          |

| 9   | <b>Deve</b><br>9.1<br>9.2                | loper Guide         Developer Tutorials         VTR Support Resources                                            |                          |

| 10  |                                          | act<br>Mailing Lists                                                                                             | <b>309</b><br>309<br>309 |

| 11  | Gloss                                    | sary                                                                                                             | 311                      |

| 12  | Publi                                    | cations & References                                                                                             | 313                      |

| 13  | Indic                                    | es and tables                                                                                                    | 315                      |

| Bil | bliogra                                  | aphy                                                                                                             | 317                      |

| Inc | dex                                      |                                                                                                                  | 321                      |

Form more information on the Verilog-to-Routing (VTR) project see VTR and VTR CAD Flow.

For documentation and tutorials on the FPGA architecture description langauge see: *FPGA Architecture Description*. For more specific documentation about VPR see *VPR*.

# CHAPTER

# ONE

# **VTR QUICK START**

This is a quick introduction to VTR which covers how to run VTR and some if its associated tools (VPR, Odin II, ABC).

# 1.1 Setting Up VTR

# 1.1.1 Download VTR

The first step is to download VTR and extract VTR on your local machine.

Note: Developers planning to modify VTR should clone the VTR git repository.

### 1.1.2 Build VTR

On most unix-like systems you can run:

> make

from the VTR root directory (hereafter referred to as \$VTR\_ROOT) to build VTR.

**Note:** In the VTR documentation lines starting with > (like > make above), indicate a command (i.e. make) to run from your terminal. When the  $\$  symbol appears at the end of a line, it indicates line continuation.

**Note:** *\$VTR\_ROOT* refers to the root directory of the VTR project source tree. To run the examples in this guide on your machine, either:

- define VTR\_ROOT as a variable in your shell (e.g. if ~/trees/vtr is the path to the VTR source tree on your machine, run the equivalent of VTR\_ROOT=~/trees/vtr in BASH) which will allow you to run the commands as written in this guide, or

- manually replace \$VTR\_ROOT in the example commandss below with your path to the VTR source tree.

Note: If VTR fails to build you may need to install the required dependencies.

For more details on building VTR on various operating systems/platforms see Building VTR.

# 1.2 Running VPR

Lets now try taking a simple pre-synthesized circuit (consisting of LUTs and Flip-Flops) and use the VPR tool to implement it on a specific FPGA architecture.

# 1.2.1 Running VPR on a Pre-Synthesized Circuit

First, lets make a directory in our home directory where we can work:

```

#Move to our home directory

> cd ~

#Make a working directory

> mkdir -p vtr_work/quickstart/vpr_tseng

#Move into the working directory

> cd ~/vtr_work/quickstart/vpr_tseng

```

Now, lets invoke the VPR tool to implement:

- the tseng circuit (\$VTR\_ROOT/vtr\_flow/benchmarks/blif/tseng.blif), on

- the EArch FPGA architecture (\$VTR\_ROOT/vtr\_flow/arch/timing/EArch.xml).

We do this by passing these files to the VPR tool, and also specifying that we want to route the circuit on a version of EArch with a routing architecture *channel width* of 100 (--route\_chan\_wdith 100):

```

> $VTR_ROOT/vpr/vpr \

$VTR_ROOT/vtr_flow/arch/timing/EArch.xml \

$VTR_ROOT/vtr_flow/benchmarks/blif/tseng.blif \

--route_chan_width 100

```

This will produce a large amount of output as VPR implements the circuit, but you should see something similar to:

```

VPR FPGA Placement and Routing.

Version: 8.1.0-dev+2b5807ecf

Revision: v8.0.0-1821-g2b5807ecf

Compiled: 2020-05-21T16:39:33

Compiler: GNU 7.3.0 on Linux-4.15.0-20-generic x86_64

Build Info: release VTR_ASSERT_LEVEL=2

University of Toronto

verilogtorouting.org

vtr-users@googlegroups.com

This is free open source code under MIT license.

#

#Lots of output trimmed for brevity....

#

Geometric mean non-virtual intra-domain period: 6.22409 ns (160.666 MHz)

Fanout-weighted geomean non-virtual intra-domain period: 6.22409 ns (160.666 MHz)

VPR suceeded

The entire flow of VPR took 3.37 seconds (max_rss 40.7 MiB)

```

which shows that VPR as successful (VPR succeeded), along with how long VPR took to run (~3 seconds in this case).

You will also see various result files generated by VPR which define the circuit implementation:

```

> ls *.net *.place *.route

tseng.net tseng.place tseng.route

```

along with a VPR log file which contains what VPR printed when last invoked:

> ls \*.log

vpr\_stdout.log

and various report files describing the characteristics of the implementation:

### **1.2.2 Visualizaing Circuit Implementation**

Note: This section requires that VPR was compiled with graphic support. See VPR Graphics for details.

The .net, .place and .route files (along with the input .blif and architecture .xml files) fully defined the circuit implementation. We can visualize the circuit implementation by:

- Re-running VPR's analysis stage (--analysis), and

- enabling VPR's graphical user interface (--*disp* on).

This is done by running the following:

```

> $VTR_ROOT/vpr/vpr \

$VTR_ROOT/vtr_flow/arch/timing/EArch.xml \

$VTR_ROOT/vtr_flow/benchmarks/blif/tseng.blif \

--route_chan_width 100 \

--analysis --disp on

```

which should open the VPR graphics and allow you to explore the circuit implementation.

As an exercise try the following:

- View the connectivity of a block (connections which drive it, and those which it drives)

- View the internals of a logic block (e.g. try to find the LUTs/.names and Flip-Flops/.latch)

- Visualize all the routed circuit connections

#### See also:

For more details on the various graphics options, see VPR Graphics

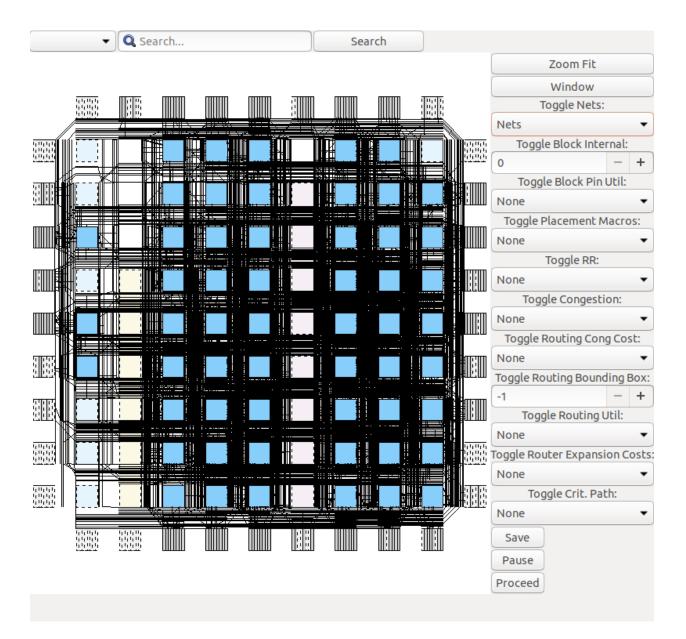

Fig. 1.1: Routed net connections of tseng on EArch.

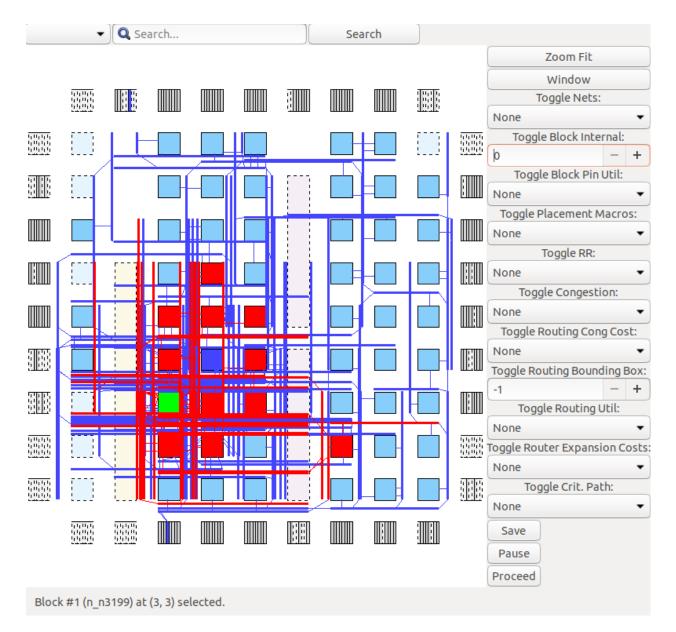

Fig. 1.2: Input (blue)/output (red) nets of block n\_n3199 (highlighted green).

**Note:** If you do not provide *--analysis*, VPR will re-implement the circuit from scratch. If you also specify *--disp* on, you can see how VPR modifies the implementation as it runs. By default *--disp* on stops at key stages to allow you to view and explore the implementation. You will need to press the Proceed button in the GUI to allow VPR to continue to the next stage.

# 1.3 Running the VTR Flow

In the previous section we have implemented a pre-synthesized circuit onto a pre-existing FPGA architecture using VPR, and visualized the result. We now turn to how we can implement *our own circuit* on a pre-existing FPGA architecture.

To do this we begin by describing a circuit behaviourly using the Verilog Hardware Description Language (HDL). This allows us to quickly and consisely define the circuit's behaviour. We will then use the VTR Flow to synthesize the behavioural Verilog description it into a circuit netlist, and implement it onto an FPGA.

# 1.3.1 Example Circuit

We will use the following simple example circuit, which causes it's output to toggle on and off:

```

Listing 1.1: blink.v ($VTR_ROOT/doc/src/quickstart/

blink.v)

```

```

//A simple cricuit which blinks an LED on and off periodically

module blink(

2

input clk,

//Input clock

3

input i_reset,

//Input active-high reset

4

output o_led); //Output to LED

5

6

//Sequential logic

7

8

//A reset-able counter which increments each clock cycle

reg[4:0] r_counter;

10

always @(posedge clk) begin

11

if (i_reset) begin //When reset is high, clear counter

12

r_counter <= 5'd0;</pre>

13

end else begin //Otherwise increment counter each clock (note that it will_

14

→overflow back to zero)

r_counter <= r_counter + 1'b1;</pre>

15

end

16

end

17

18

//Combinational logic

19

20

//Drives o_led high if count is below a threshold

21

always @(*) begin

22

if (r_counter < 5'd16) begin</pre>

23

o_led <= 1'b1;

24

end else begin

25

o_led <= 1'b0;</pre>

26

end

27

end

28

```

(continues on next page)

29 30 (continued from previous page)

```

endmodule

```

This Verilog creates a sequential 5-bit register  $(r\_counter)$  which increments every clock cycle. If the count is below 16 it drives the output  $(o\_led)$  high, otherwise it drives it low.

# 1.3.2 Manually Running the VTR Flow

Lets start by making a fresh directory for us to work in:

```

> mkdir -p ~/vtr_work/quickstart/blink_manual

> cd ~/vtr_work/quickstart/blink_manual

```

Next we need to run the three main sets of tools:

- *Odin II* performs 'synthesis' which converts our behavioural Verilog (.v file) into a circuit netlist (.blif file) consisting of logic equations and FPGA architecture primitives (Flip-Flops, adders etc.),

- *ABC* performs 'logic optimization' which simplifies the circuit logic, and 'technology mapping' which converts logic equations into the Look-Up-Tables (LUTs) available on an FPGA, and

- *VPR* which performs packing, placement and routing of the circuit to implement it on the targetted FPGA architecture.

### Synthesizing with ODIN II

First we'll run ODIN II on our Verilog file to synthesize it into a circuit netlist, providing the options:

- -a \$VTR\_ROOT/vtr\_flow/arch/timing/EArch.xml which specifies what FPGA architecture we are targetting,

- -V \$VTR\_ROOT/doc/src/quickstart/blink.v which specifies the verilog file we want to synthesize, and

- -o blink.odin.blif which specifies the name of the generated .blif circuit netlist.

The resulting command is:

```

> $VTR_ROOT/ODIN_II/odin_II \

-a $VTR_ROOT/vtr_flow/arch/timing/EArch.xml \

-V $VTR_ROOT/doc/src/quickstart/blink.v \

-o blink.odin.blif

```

which when run should end with something like:

```

Total time: 14.7ms

Odin ran with exit status: 0

Odin II took 0.01 seconds (max_rss 5.1 MiB)

```

where Odin ran with exit status: 0 indicates Odin successfully synthesized our verilog.

We can now take a look at the circuit which ODIN produced (blink.odin.blif). The file is long and likely harder to follow than our code in blink.v; however it implements the same functionality. Some interesting highlights are shown below:

Listing 1.2: Instantiations of rising-edge triggered Latches (i.e. Flip-Flops) in blink.odin.blif (implements part of r\_counter in blink.v)

```

.latch blink^nMUX~0^MUX_2~23 blink^r_counter~0_FF re blink^clk 3

.latch blink^nMUX~0^MUX_2~27 blink^r_counter~4_FF re blink^clk 3

```

Listing 1.3: Adder primitive instantiations in blink.odin.blif, used to perform addition (implements part of the + operator in blink.v)

```

.subckt adder a[0]=blink^r_counter~0_FF b[0]=vcc cin[0]=blink^ADD~2-0[0]\

cout[0]=blink^ADD~2-1[0] sumout[0]=blink^ADD~2-1[1]

.subckt adder a[0]=blink^r_counter~1_FF b[0]=gnd cin[0]=blink^ADD~2-1[0]\

cout[0]=blink^ADD~2-2[0] sumout[0]=blink^ADD~2-2[1]

```

Listing 1.4: Logic equation (.names truth-table) in blink.odin. blif, implementing logical OR (implements part of the < operator in blink.v)

```

.names blink^LT~4^GT~10 blink^LT~4^GT~12 blink^LT~4^GT~14 blink^LT~4^GT~16 blink^LT~4^

GT~18 blink^LT~4^1OR~9

1---- 1

-1--- 1

--1-- 1

----1 1

```

#### See also:

For more information on the BLIF file format see BLIF Netlist (.blif).

#### **Optimizing and Technology Mapping with ABC**

Next, we'll optimize and technology map our circuit using ABC, providing the option:

• -c <script>, where <script> is a set of commands telling ABC how to synthesize our circuit.

We'll use the following, simple ABC commands:

| read blink.odin.blif;                             | #Read the circuit synthesized by_ |

|---------------------------------------------------|-----------------------------------|

| ⇔ODIN                                             |                                   |

| <b>if</b> -K 6;                                   | #Technology map to 6 input LUTs_  |

| $\hookrightarrow (6-LUTs)$                        |                                   |

| write_hie blink.odin.blif blink.abc_no_clock.blif | #Write new circuit to blink.abc_  |

| ⇔no_clock.blif                                    |                                   |

**Note:** Usually you should use a more complicated script (such as that used by *run\_vtr\_flow*) to ensure ABC optitmizes your circuit well.

The corresponding command to run is:

(continued from previous page)

When run, ABC's output should look similar to:

```

ABC command line: "read blink.odin.blif; if -K 6; write_hie blink.odin.blif blink.abc_

→no_clock.blif".

Hierarchy reader converted 6 instances of blackboxes.

The network was strashed and balanced before FPGA mapping.

Hierarchy writer reintroduced 6 instances of blackboxes.

```

If we now inspect the produced BLIF file (blink.abc\_no\_clock.blif) we see that ABC was able to significantly simplify and optimize the circuit's logic (compared to blink.odin.blif):

| Listing | 1.5: | blink.abc | no | _clock.blif |

|---------|------|-----------|----|-------------|

|---------|------|-----------|----|-------------|

```

# Benchmark "blink" written by ABC on Tue May 19 15:42:50 2020

1

.model blink

2

.inputs blink^clk blink^i_reset

3

.outputs blink^o_led

4

5

.latch

n19 blink^r_counter~0_FF 2

6

n24 blink^r_counter~4_FF 2

.latch

7

n29 blink^r_counter~3_FF 2

.latch

8

n34 blink^r_counter~2_FF 2

.latch

9

.latch

n39 blink^r_counter~1_FF 2

10

11

12

.subckt adder a[0]=blink^r_counter~0_FF b[0]=vcc cin[0]=blink^ADD~2-0[0]_

13

⇔cout[0]=blink^ADD~2-1[0] sumout[0]=blink^ADD~2-1[1]

.subckt adder a[0]=blink^r_counter~1_FF b[0]=gnd cin[0]=blink^ADD~2-1[0]_

14

→cout[0]=blink^ADD~2-2[0] sumout[0]=blink^ADD~2-2[1]

.subckt adder a[0]=blink^r_counter~2_FF b[0]=gnd cin[0]=blink^ADD~2-2[0]_

15

where the second [0] = blink^ADD ~ 2 - 3[0] sumout [0] = blink^ADD ~ 2 - 3[1]

.subckt adder a[0]=blink^r_counter~3_FF b[0]=gnd cin[0]=blink^ADD~2-3[0]_

16

\leftrightarrow cout[0]=blink^ADD~2-4[0] sumout[0]=blink^ADD~2-4[1]

.subckt adder a[0]=blink^r_counter~4_FF b[0]=gnd cin[0]=blink^ADD~2-4[0]_

17

→cout[0]=blink^ADD~2-5[0] sumout[0]=blink^ADD~2-5[1]

.subckt adder a[0]=gnd b[0]=gnd cin[0]=unconn cout[0]=blink^ADD~2-0[0]

18

→sumout[0]=blink^ADD~2-0~dummy_output~0~1

19

20

.names blink^i_reset blink^ADD~2-1[1] n19

21

01 1

22

.names blink^i_reset blink^ADD~2-5[1] n24

23

01 1

24

.names blink^i_reset blink^ADD~2-4[1] n29

25

01 1

26

.names blink^i_reset blink^ADD~2-3[1] n34

27

01 1

28

.names blink^i_reset blink^ADD~2-2[1] n39

29

01 1

30

.names vcc

31

1

32

.names gnd

33

0

34

.names unconn

35

```

(continued from previous page)

```

0

.names blink^r_counter~4_FF blink^o_led

0 1

.end

.model adder

.inputs a[0] b[0] cin[0]

.outputs cout[0] sumout[0]

.blackbox

.end

```

ABC has kept the .latch and .subckt adder primitives, but has significantly simplified the other logic (. names).

However, there is an issue with the above BLIF produced by ABC: the latches (rising edge Flip-Flops) do not have any clocks or edge sensitivity specified, which is information required by VPR.

#### **Re-inserting clocks**

36

37

38

39 40 41

42

43

44

45

46

We will restore the clock information by running a script which will transfer that information from the original ODIN BLIF file (writing it to the new file blink.pre-vpr.blif):

```

> $VTR_ROOT/vtr_flow/scripts/restore_multiclock_latch.pl \

blink.odin.blif \

blink.abc_no_clock.blif \

blink.pre-vpr.blif

```

If we inspect blink.pre-vpr.blif we now see that the clock (blink^clk) has been restored to the Flip-Flops:

```

> grep 'latch' blink.pre-vpr.blif

.latch n19 blink^r_counter~0_FF re blink^clk 3

.latch n24 blink^r_counter~4_FF re blink^clk 3

.latch n29 blink^r_counter~3_FF re blink^clk 3

.latch n34 blink^r_counter~2_FF re blink^clk 3

.latch n39 blink^r_counter~1_FF re blink^clk 3

```

#### Implementing the circuit with VPR

Now that we have the optimized and technology mapped netlist (blink.pre-vpr.blif), we can invoke VPR to implement it onto the EArch FPGA architecture (in the same way we did with the tseng design earlier). However, since our BLIF file doesn't match the design name we explicitly specify:

- blink as the circuit name, and

- the input circuit file with *--circuit\_file*.

to ensure the resulting .net, .place and .route files will have the correct names.

The resulting command is:

```

> $VTR_ROOT/vpr/vpr \

$VTR_ROOT/vtr_flow/arch/timing/EArch.xml \

```

(continues on next page)

(continued from previous page)

```

blink --circuit_file blink.pre-vpr.blif \

--route_chan_width 100

```

and after VPR finishes we should see the resulting implementation files:

> ls \*.net \*.place \*.route

blink.net blink.place blink.route

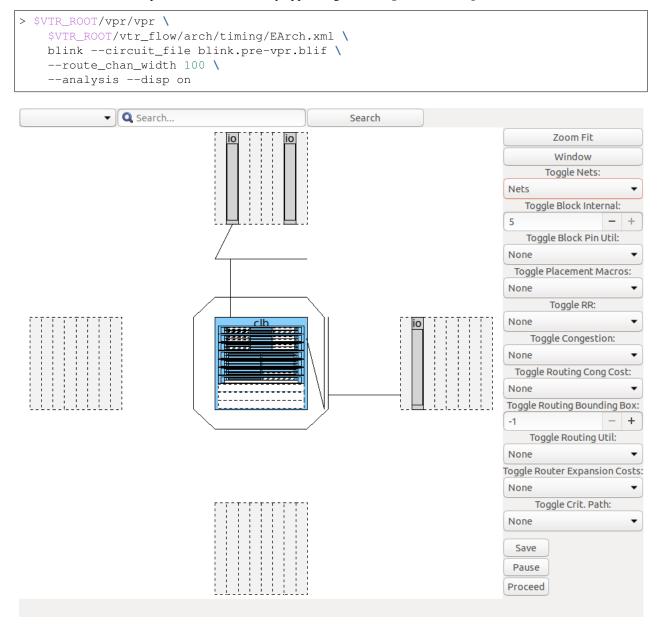

We can then view the implementation as usual by appending --analysis --disp on to the command:

Fig. 1.3: blink.v circuit implementation on the EArch FPGA architecture as viewed in the VPR GUI

# 1.3.3 Automatically Running the VTR Flow

Running each stage of the flow manually is time consuming (and potentially error prone). For convenience, VTR provides a script (*run\_vtr\_flow*) which automates this process.

Lets make a new directory to work in named blink\_run\_flow:

```

> mkdir -p ~/vtr_work/quickstart/blink_run_flow

> cd ~/vtr_work/quickstart/blink_run_flow

```

Now lets run the script (\$VTR\_ROOT/vtr\_flow/scripts/run\_vtr\_flow.pl) passing in:

- The circuit verilog file (\$VTR\_ROOT/doc/src/quickstart/blink.v)

- The FPGA architecture file (\$VTR\_ROOT/vtr\_flow/arch/timing/EArch.xml)

and also specifying the options:

- -temp\_dir . to run in the current directory (. on unix-like systems)

- --route\_chan\_width 100 a fixed FPGA routing architecture channel width.

The resulting command is:

```

> $VTR_ROOT/vtr_flow/scripts/run_vtr_flow.pl \

$VTR_ROOT/doc/src/quickstart/blink.v \

$VTR_ROOT/vtr_flow/arch/timing/EArch.xml \

-temp_dir . \

--route_chan_width 100

```

Note: Options unrecognized by run\_vtr\_flow (like --route\_chan\_width) are passed on to VPR.

which should produce output similar to:

| EArch/blink | OK | (took 0.26 seconds) |

|-------------|----|---------------------|

|-------------|----|---------------------|

There are also multiple log files (including for ABC, ODIN and VPR), which by convention the script names with the .out suffix:

With the main log files of interest including the ODIN log file (odin.out), log files produced by ABC (e.g. abc0. out), and the VPR log file (vpr.out).

**Note:** ABC may be invoked multiple times if a circuit has multiple clock domains, producing multiple log files (abc0.out, abc1.out, ...)

You will also see there are several BLIF files produced:

```

> ls *.blif

0_blink.abc.blif 0_blink.raw.abc.blif blink.odin.blif

0_blink.odin.blif blink.abc.blif blink.pre-vpr.blif

```

With the main files of interest being blink.odin.blif (netlist produced by ODIN), blink.abc.blif (final netlist produced by ABC after clock restoration), blink.pre-vpr.blif netlist used by VPR (usually identical to blink.abc.blif).

Like before, we can also see the implementation files generated by VPR:

> ls \*.net \*.place \*.route

blink.net blink.place blink.route

which we can visualize with:

```

> $VTR_ROOT/vpr/vpr \

$VTR_ROOT/vtr_flow/arch/timing/EArch.xml \

blink --circuit_file blink.pre-vpr.blif \

--route_chan_width 100 \

--analysis --disp on

```

# 1.4 Next Steps

Now that you've finished the VTR quickstart, you're ready to start experimenting and using VTR.

Here are some possible next steps for users wishing to use VTR:

- Try modifying the Verilog file (e.g. blink.v) or make your own circuit and try running it through the flow.

- Learn about FPGA architecture modelling (*Tutorials, Reference*), and try modifying a copy of EArch to see how it changes the implementation of blink.v.

- Read more about the VTR CAD Flow, and Task automation framework.

- Find out more about using other benchmark sets, like how to run the Titan Benchmark Suite.

- Discover how to generate FASM for bitstream creation.

- Suggest or make enhancements to VTR's documentation.

Here are some possible next steps for developers wishing to modify and improve VTR:

- Try the next steps listed for users above to learn how VTR is used.

- Work through the new developer tutorial.

- Read through the *developer guide*.

- Look for open issues to which you can contribute.

- Begin exploring the source code for the main tools in VTR (e.g. VPR in *SVTR\_ROOT/vpr/src*).

#### # Building VTR #

## Overview ##

VTR uses [CMake](https://cmake.org) as it's build system.

CMake provides a portable cross-platform build systems with many useful features.

## Tested Compilers ## VTR requires a C++-14 compliant compiler. The following compilers are tested with VTR:

- GCC/G++: 5, 6, 7, 8, 9

- Clang/Clang++: 3.8, 6

Other compilers may work but are untested (your milage may vary).

## Unix-like ## For unix-like systems we provide a wrapper Makefile which supports the traditional *make* and *make clean* commands, but calls CMake behind the scenes.

### Dependencies ###

For the basic tools you need:

- Bison & Flex

- cmake, make

- A modern C++ compiler supporting C++14 (such as GCC >= 4.9 or clang >= 3.6)

#### For the VPR GUI you need:

- Cairo

- FreeType

- Xft (libXft + libX11)

- fontconfig

- libgtk-3-dev

#### For the [regression testing and benchmarking](README.developers.md#running-tests) you will need:

- Perl + List::MoreUtils

- Python

- time

#### It is also recommended you install the following development tools:

- git

- ctags

- gdb

- valgrind

- clang-format-7

#### For Docs generation you will need:

- Doxygen

- python-sphinx

- python-sphinx-rtd-theme

- python-recommonmark

#### Debian & Ubuntu ####

The following should be enough to get the tools, VPR GUI and tests going on a modern Debian or Ubuntu system:

```shell apt-get install

build-essential flex bison cmake fontconfig libcairo2-dev libfontconfig1-dev libx11-dev libxft-dev libgtk-3-dev perl liblist-moreutils-perl python time

•••

For documentation generation these additional packages are required:

```shell apt-get install

doxygen python-sphinx python-sphinx-rtd-theme python-recommonmark

•••

For development the following additional packages are useful:

```shell apt-get install

git valgrind gdb ctags

•••

```

#### Using Nix ####

```

Although the recommended platform is Debian or Ubuntu, Nix can be used to build VTR on other platforms, such as MacOS.

If you don't have [Nix](https://nixos.org/nix/), you can [get it](https://nixos.org/nix/download.html) with:

`shell \$ curl -L https://nixos.org/nix/install | sh `

These commands will set up dependencies for Linux and MacOS and build VTR:

`shell #In the VTR root \$ nix-shell dev/nix/shell.nix \$ make `

### Building using the Makefile wrapper ### Run make from the root of the VTR source tree

`shell #In the VTR root \$ make ... [100%] Built target vpr `

#### Specifying the build type #### You can specify the build type by passing the BUILD\_TYPE parameter.

For instance to create a debug build (no optimization and debug symbols):

`shell #In the VTR root \$ make BUILD\_TYPE=debug ... [100%] Built target vpr `

#### Passing parameters to CMake #### You can also pass parameters to CMake.

For instance to set the CMake configuration variable VTR\_ENABLE\_SANITIZE on:

`shell #In the VTR root \$ make CMAKE\_PARAMS="-DVTR\_ENABLE\_SANITIZE=ON" ...

[100%] Built target vpr `

Both the BUILD\_TYPE and CMAKE\_PARAMS can be specified concurrently: `shell #In the VTR root \$ make BUILD\_TYPE=debug CMAKE\_PARAMS="-DVTR\_ENABLE\_SANITIZE=ON" ... [100%] Built target vpr `

### Using CMake directly ### You can also use cmake directly.

First create a build directory under the VTR root:

```shell #In the VTR root \$ mkdir build \$ cd build

#Call cmake pointing to the directory containing the root CMakeLists.txt \$ cmake ..

#Build \$ make ```

#### Changing configuration on the command line #### You can change the CMake configuration by passing command line parameters.

For instance to set the configuration to debug:

```shell #In the build directory \$ cmake . -DCMAKE\_BUILD\_TYPE=debug

#Re-build \$ make ```

#### Changing configuration interactively with ccmake #### You can also use *ccmake* to to modify the build configuration.

```shell #From the build directory \$ ccmake . #Make some configuration change

#Build \$ make ```

## Other platforms ##

CMake supports a variety of operating systems and can generate project files for a variety of build systems and IDEs. While VTR is developed primarily on Linux, it should be possible to build on different platforms (your milage may vary). See the [CMake documentation](https://cmake.org) for more details about using cmake and generating project files on other platforms and build systems (e.g. Eclipse, Microsoft Visual Studio).

### Microsoft Windows ###

NOTE: VTR support on Microsoft Windows is considered experimental

#### Cygwin #### [Cygwin](https://www.cygwin.com/) provides a POSIX (i.e. unix-like) environment for Microsoft Windows.

From within the cygwin terminal follow the Unix-like build instructions listed above.

Note that the generated executables will rely upon Cygwin (e.g. cygwin1.dll) for POSIX compatibility.

#### Cross-compiling from Linux to Microsoft Windows with MinGW-W64 #### It is possible to cross-compile from a Linux host system to generate Microsoft Windows executables using the [MinGW-W64](https://mingw-w64.org) compilers. These can usually be installed with your Linux distribution's package manager (e.g. *sudo apt-get install mingw-w64* on Debian/Ubuntu).

Unlike Cygwin, MinGW executables will depend upon the standard Microsoft Visual C++ run-time.

To build VTR using MinGW: ``shell #In the VTR root \$ mkdir build\_win64 \$ cd build\_win64

#Run cmake specifying the toolchain file to setup the cross-compilation environment \$ cmake .. - DCMAKE\_TOOLCHAIN\_FILE ../cmake/toolchains/mingw-linux-cross-compile-to-windows.cmake

#Building will produce Windows executables \$ make ```

Note that by default the MS Windows target system will need to dynamically link to the *libgcc* and *libstdc*++ DLLs. These are usually found under /usr/lib/gcc on the Linux host machine.

See the [toolchain file](cmake/toolchains/mingw-linux-cross-compile-to-windows.cmake) for more details.

#### Microsoft Visual Studio #### CMake can generate a Microsft Visual Studio project, enabling VTR to be built with the Microsoft Visual C++ (MSVC) compiler.

##### Installing additional tools ##### VTR depends on some external unix-style tools during it's buid process; in particular the *flex* and *bison* parser generators.

One approach is to install these tools using [MSYS2](http://www.msys2.org/), which provides up-to-date versions of many unix tools for MS Windows.

To ensure CMake can find the *flex* and *bison* executables you must ensure that they are available on your system path. For instance, if MSYS2 was installed to *C:msys64* you would need to ensure that *C:msys64usrbin* was included in the system PATH environment variable.

##### Generating the Visual Studio Project ##### CMake (e.g. the *cmake-gui*) can then be configured to generate the MSVC project.

### CHAPTER

# TWO

# VTR

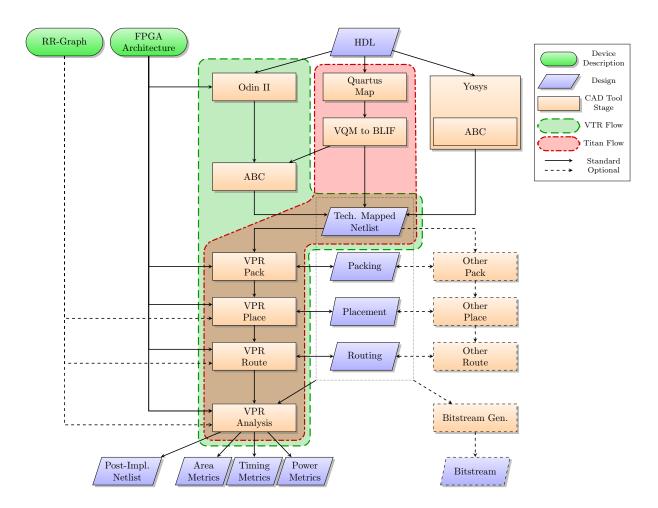

The Verilog-to-Routing (VTR) project [RLY+12][LAK+14] is a world-wide collaborative effort to provide a opensource framework for conducting FPGA architecture and CAD research and development. The VTR design flow takes as input a Verilog description of a digital circuit, and a description of the target FPGA architecture.

It then perfoms:

- Elaboration & Synthesis (Odin II)

- Logic Optimization & Technology Mapping (ABC)

- Packing, Placement, Routing & Timing Analysis (VPR)

Generating FPGA speed and area results.

VTR also includes a set of benchmark designs known to work with the design flow.

# 2.1 VTR CAD Flow

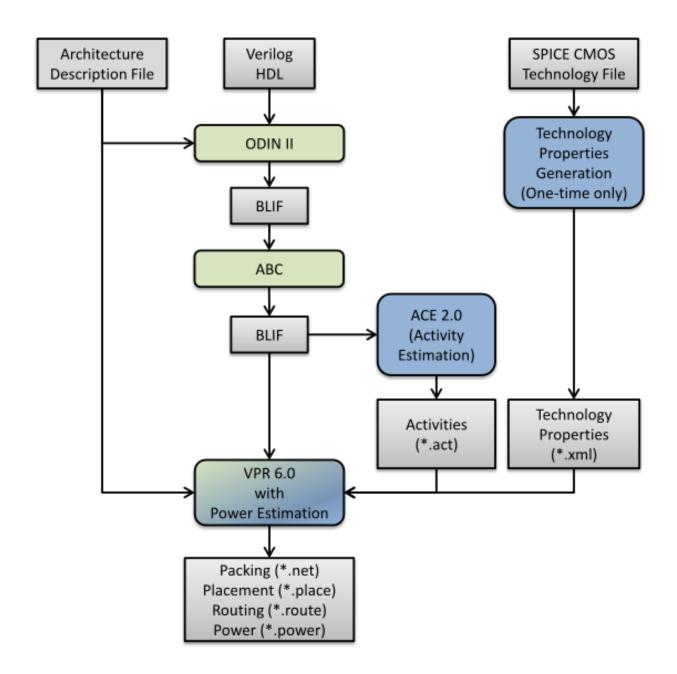

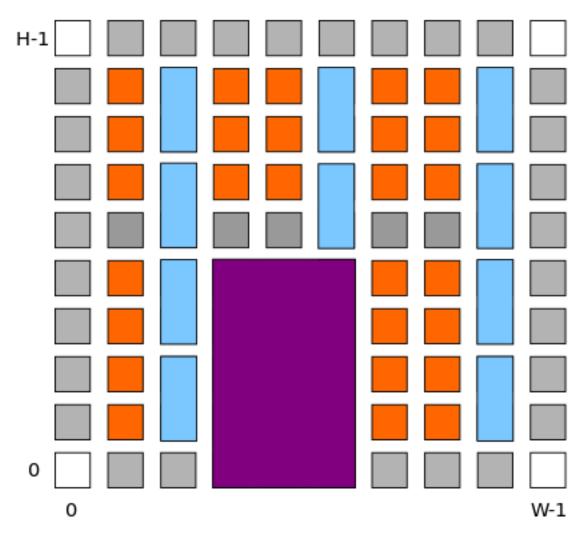

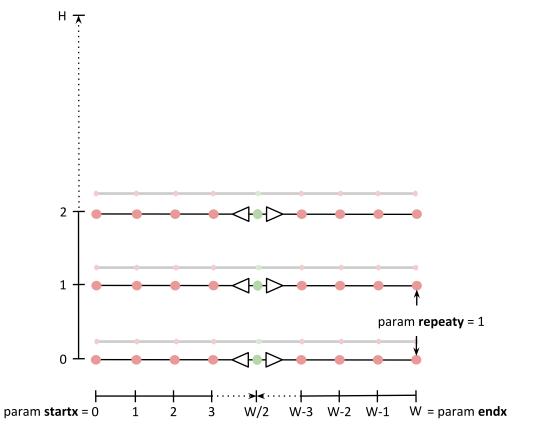

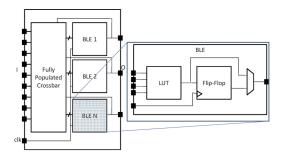

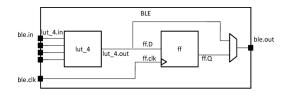

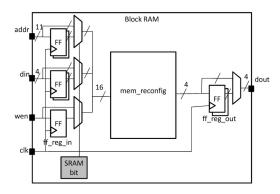

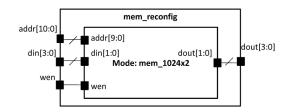

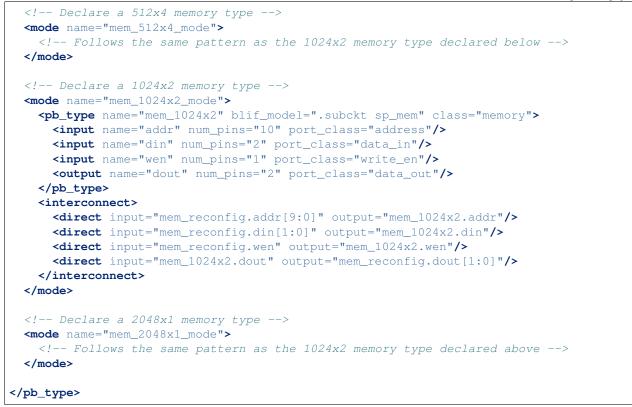

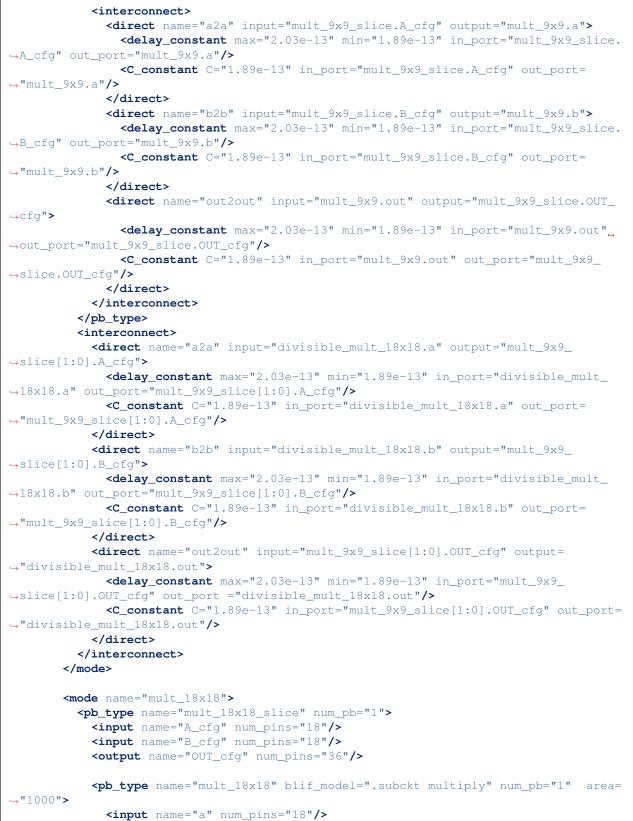

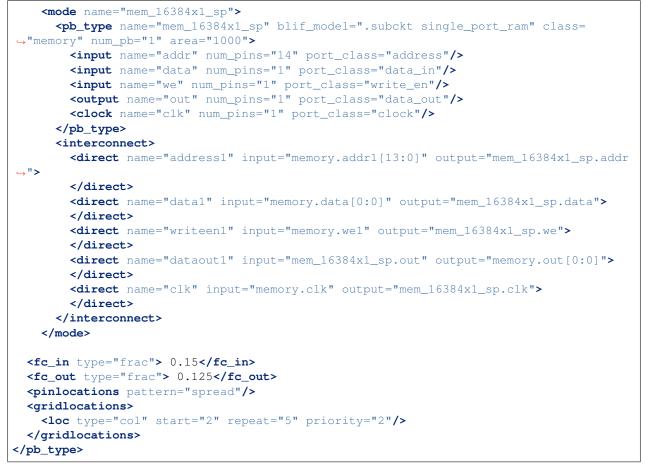

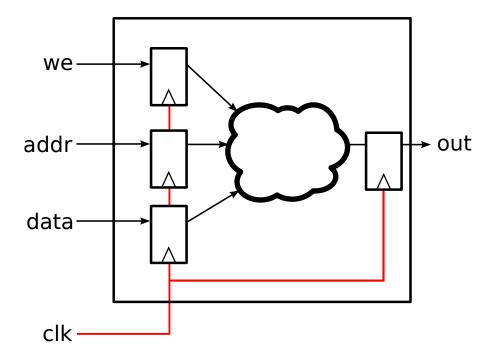

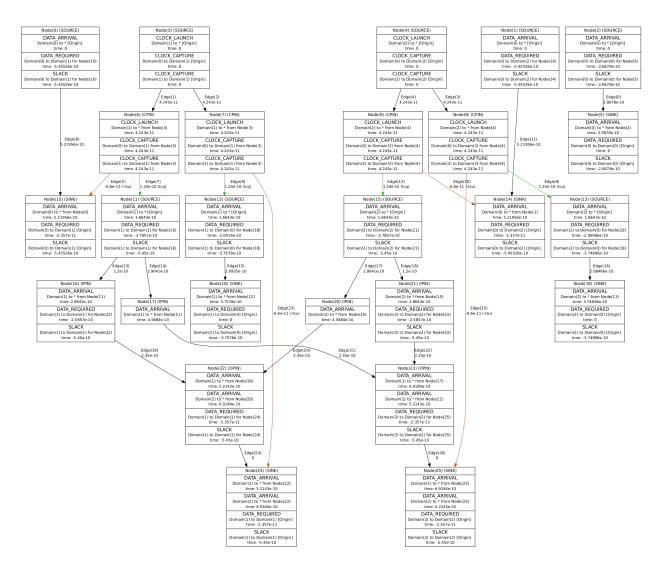

In the standard VTR Flow (Fig. 2.1), *Odin II* converts a Verilog Hardware Destription Language (HDL) design into a flattened netlist consisting of logic gates, flip-flops, and blackboxes representing heterogeneous blocks (e.g. adders, multipliers, RAM slices) [JKGS10].

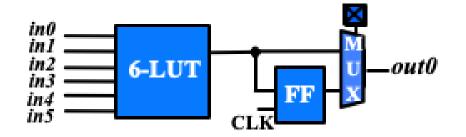

Next, the *ABC* synthesis package is used to perform technology-independent logic optimization, and technology-maps the circuit into LUTs [SG][PHMB07][CCMB07]. The output of ABC is a *.blif format* netlist of LUTs, flip flops, and blackboxes.

*VPR* then packs this netlist into more coarse-grained logic blocks, places and then routes the circuit [BRM99][Bet98][BR96a][BR96b][BR97b][BR97a][MBR99][MBR00][BR00]. Generating *output files* for each stage. VPR will analyze the resulting implementation, producing various statistics such as the minimum number of tracks per channel required to successfully route, the total wirelength, circuit speed, area and power. VPR can also produce a post-implementation netlist for simulation and formal verification.

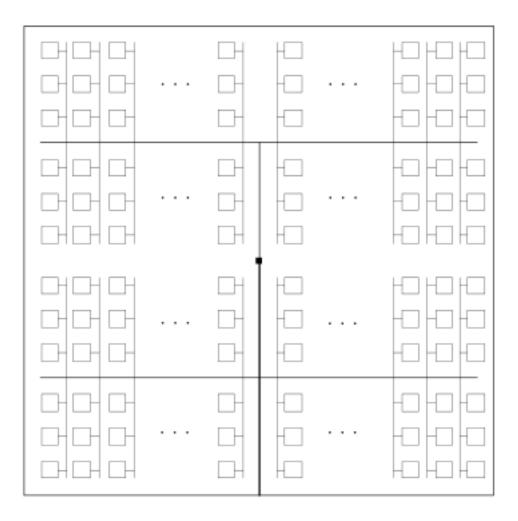

Fig. 2.1: VTR CAD flow (and variants)

# 2.1.1 CAD Flow Variations

### **Titan CAD Flow**

The Titan CAD Flow [MWL+13][MWL+15] interfaces Intel's Quartus tool with VPR. This allows designs requiring industrial strength language coverage and IP to be brought into VPR.

### **Other CAD Flow Variants**

Many other CAD flow variations are possible.

For instance, it is possible to use other logic synthesis tools like Yosys [Wol] to generate the design netlist. One could also use logic optimizers and technology mappers other than ABC; just put the output netlist from your technology-mapper into .blif format and pass it into VPR.

It is also possible to use tools other than VPR to perform the different stages of the implementation.

For example, if the logic block you are interested in is not supported by VPR, your CAD flow can bypass VPR's packer by outputting a netlist of logic blocks in *.net format*. VPR can place and route netlists of any type of logic block – you simply have to create the netlist and describe the logic block in the FPGA architecture description file.

Similarly, if you want only to route a placement produced by another CAD tool you can create a *.place file*, and have VPR route this pre-existing placement.

If you only need to analyze an implementation produced by another tool, you can create a *.route file*, and have VPR analyze the implementation, to produce area/delay/power results.

Finally, if your routing architecture is not supported by VPR's architecture generator, you can describe your routing architecture in an *rr\_graph.xml file*, which can be loaded directly into VPR.

# 2.1.2 Bitstream Generation

The technology mapped netlist and packing/placement/routing results produced by VPR contain the information needed to generate a device programming bitstreams.

VTR focuses on the core physical design optimization tools and evaluation capabilities for new architectures and does not directly support generating device programming bitstreams. Bitstream generators can either ingest the implementation files directly or make use of VTR utilities to emit *FASM*.

# 2.2 Get VTR

# 2.2.1 How to Cite

Citations are important in academia, as they ensure contributors recieve credit for their efforts. Therefore please use the following paper as a general citation whenever you use VTR:

K. E. Murray, O. Petelin, S. Zhong, J. M. Wang, M. ElDafrawy, J.-P. Legault, E. Sha, A. G. Graham, J. Wu, M. J. P. Walker, H. Zeng, P. Patros, J. Luu, K. B. Kent and V. Betz "VTR 8: High Performance CAD and Customizable FPGA Architecture Modelling", ACM TRETS, 2020

Bibtex:

| @article{vtr8,                                                                                    |

|---------------------------------------------------------------------------------------------------|

| title={VTR 8: High Performance CAD and Customizable FPGA Architecture Modelling},                 |

| author={Murray, Kevin E. and Petelin, Oleg and Zhong, Sheng and Wang, Jai Min and                 |

| ightarrowElDafrawy, Mohamed and Legault, Jean-Philippe and Sha, Eugene and Graham, Aaron G.       |

| $\rightarrow$ and Wu, Jean and Walker, Matthew J. P. and Zeng, Hanging and Patros, Panagiotis and |

| $\rightarrow$ Luu, Jason and Kent, Kenneth B. and Betz, Vaughn},                                  |

| journal={ACM Trans. Reconfigurable Technol. Syst.},                                               |

| year={2020}                                                                                       |

|                                                                                                   |

We are always interested in how VTR is being used, so feel free email the vtr-users list with how you are using VTR.

# 2.2.2 Download

The official VTR release is available from:

https://verilogtorouting.org/download

### 2.2.3 Release

The VTR 8.1 release provides the following:

- benchmark circuits,

- sample FPGA architecture description files,

- the full CAD flow, and

- scripts to run that flow.

The FPGA CAD flow takes as input, a user circuit (coded in Verilog) and a description of the FPGA architecture. The CAD flow then maps the circuit to the FPGA architecture to produce, as output, a placed-and-routed FPGA. Here are some highlights of the 8.1 full release:

- Timing-driven logic synthesis, packing, placement, and routing with multi-clock support.

- Power Analysis

- Benchmark digital circuits consisting of real applications that contain both memories and multipliers.

Seven of the 19 circuits contain more than 10,000 6-LUTs. The largest of which is just under 100,000 6-LUTs.

- Sample architecture files of a wide range of different FPGA architectures including:

- 1. Timing annotated architectures

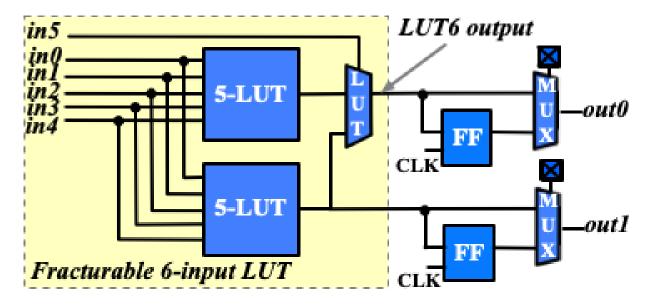

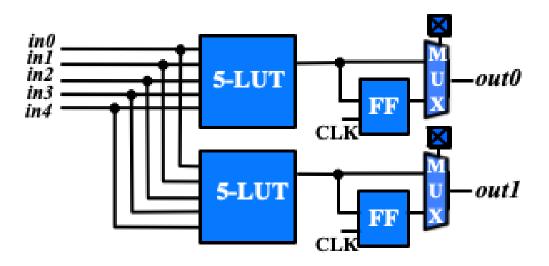

- 2. Various fracturable LUTs (dual-output LUTs that can function as one large LUT or two smaller LUTs with some shared inputs)

- 3. Various configurable embedded memories and multiplier hard blocks

- 4. One architecture containing embedded floating-point cores, and

- 5. One architecture with carry chains.

- A front-end Verilog elaborator that has support for hard blocks.

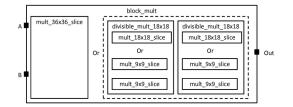

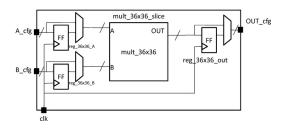

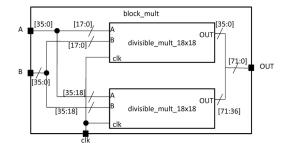

This tool can automatically recognize when a memory or multiplier instantiated in a user circuit is too large for a target FPGA architecture. When this happens, the tool can automatically split that memory/multiplier into multiple smaller components (with some glue logic to tie the components together). This makes it easier to investigate different hard block architectures because one does not need to modify the Verilog if the circuit instantiates a memory/multiplier that is too large.

• Packing/Clustering support for FPGA logic blocks with widely varying functionality.

This includes memories with configurable aspect ratios, multipliers blocks that can fracture into smaller multipliers, soft logic clusters that contain fracturable LUTs, custom interconnect within a logic block, and more.

- Ready-to-run scripts that guide a user through the complexities of building the tools as well as using the tools to map realistic circuits (written in Verilog) to FPGA architectures.

- Regression tests of experiments that we have conducted to help users error check and/or compare their work.

Along with experiments for more conventional FPGAs, we also include an experiment that explores FPGAs with embedded floating-point cores investigated in [HYL+09] to illustrate the usage of the VTR framework to explore unconventional FPGA architectures.

### 2.2.4 Development Trunk

The development trunk for the Verilog-to-Routing project is hosted at:

https://github.com/verilog-to-routing/vtr-verilog-to-routing

Unlike the nicely packaged offical releases the code in a constant state of flux. You should expect that the tools are not always stable and that more work is needed to get the flow to run.

# 2.3 Install VTR

- 1. Download the VTR release

- 2. Unpack the release in a directory of your choice (herafter referred to as \$VTR\_ROOT)

- 3. Navigate to \$VTR\_ROOT and run

make

which will build all the required tools.

Warning: \$VTR\_ROOT should be replaced with the path to the root of VTR source tree on your machine.

The complete VTR flow has been tested on 64-bit Linux systems. The flow should work in other platforms (32-bit Linux, Windows with cygwin) but this is untested.

#### See also:

More information about building VTR can be found in the Developer Guide

Please let us know your experience with building VTR so that we can improve the experience for others.

The tools included official VTR releases have been tested for compatibility. If you download a different version of those tools, then those versions may not be mutually compatible with the VTR release.

# 2.3.1 Verifying Installation

To verfiy that VTR has been installed correctly run:

```

$VTR_ROOT/vtr_flow/scripts/run_vtr_task.pl basic_flow

```

The expected output is:

k6\_N10\_memSize16384\_memData64\_40nm\_timing/ch\_intrinsics...OK

# 2.4 Running the VTR Flow

VTR is a collection of tools that perform the full FPGA CAD flow from Verilog to routing.

The design flow consists of:

- Odin II (Logic Synthesis)

- *ABC* (Logic Optimization & Technology Mapping)

- VPR (Pack, Place & Route)

There is no single executable for the entire flow.

Instead, scripts are provided to allow the user to easily run the entire tool flow. The following provides instructions on using these scripts to run VTR.

# 2.4.1 Running a Single Benchmark

The run\_vtr\_flow script is provided to execute the VTR flow for a single benchmark and architecture.

Note: In the following \$VTR\_ROOT means the root directory of the VTR source code tree.

```

$VTR_ROOT/vtr_flow/scripts/run_vtr_flow.pl <circuit_file> <architecture_file>

```

It requires two arguments:

- <circuit\_file> A benchmark circuit, and

- <architecture\_file> an FPGA architecture file

Circuits can be found under:

\$VTR\_ROOT/vtr\_flow/benchmarks/

Architecture files can be found under:

\$VTR\_ROOT/vtr\_flow/arch/

The script can also be used to run parts of the VTR flow.

#### See also:

*run\_vtr\_flow* for the detailed command line options of run\_vtr\_flow.pl.

# 2.4.2 Running Multiple Benchmarks & Architectures with Tasks

VTR also supports *tasks*, which manage the execution of the VTR flow for multiple benchmarks and architectures. By default, tasks execute the *run\_vtr\_flow* for every circuit/architecture combination.

VTR provides a variety of standard tasks which can be found under:

\$VTR\_ROOT/vtr\_flow/tasks

Tasks can be executed using *run\_vtr\_task*:

\$VTR\_ROOT/vtr\_flow/scripts/run\_vtr\_task.pl <task\_name>

#### See also:

run\_vtr\_task for the detailed command line options of run\_vtr\_task.pl.

#### See also:

Tasks for more information on creating, modifying and running tasks.

# 2.4.3 Extracting Information & Statistics

VTR can also extract useful information and statistics from executions of the flow such as area, speed tool execution time etc.

For single benchmarks *parse\_vtr\_flow* extrastics statistics from a single execution of the flow.

For a *Task*, *parse\_vtr\_task* can be used to parse and assemble statistics for the entire task (i.e. multiple circuits and architectures).

For regression testing purposes these results can also be verified against a set of *golden* reference results. See *parse\_vtr\_task* for details.

# 2.5 Benchmarks

There are several sets of benchmark designs which can be used with VTR.

### 2.5.1 VTR Benchmarks

The VTR benchmarks [RLY+12][LAK+14] are a set of medium-sized benchmarks included with VTR. They are fully compatible with the full VTR flow. They are suitable for FPGA architecture research and medium-scale CAD research.

| Benchmark        | Domain            |

|------------------|-------------------|

| bgm              | Finance           |

| blob_merge       | Image Processing  |

| boundtop         | Ray Tracing       |

| ch_intrinsics    | Memory Init       |

| diffeq1          | Math              |

| diffeq2          | Math              |

| LU8PEEng         | Math              |

| LU32PEEng        | Math              |

| mcml             | Medical Physics   |

| mkDelayWorker32B | Packet Processing |

| mkPktMerge       | Packet Processing |

| mkSMAdapter4B    | Packet Processing |

| or1200           | Soft Processor    |

| raygentop        | Ray Tracing       |

| sha              | Cryptography      |

| stereovision0    | Computer Vision   |

| stereovision1    | Computer Vision   |

| stereovision2    | Computer Vision   |

| stereovision3    | Computer Vision   |

| •                |                   |

Table 2.1: The VTR 7.0 Benchmarks.

The VTR benchmarks are provided as Verilog under:

```

$VTR_ROOT/vtr_flow/benchmarks/verilog

```

This provides full flexibility to modify and change how the designs are implemented (including the creation of new netlist primitives).

The VTR benchmarks are also included as pre-synthesized BLIF files under:

```

$VTR_ROOT/vtr_flow/benchmarks/vtr_benchmarks_blif

```

### 2.5.2 Titan Benchmarks

The Titan benchmarks [MWL+13][MWL+15] are a set of large modern FPGA benchmarks. The pre-synthesized versions of these benchmarks are compatible with recent versions of VPR.

The Titan benchmarks are suitable for large-scale FPGA CAD research, and FPGA architecture research which does not require synthesizing new netlist primitives.

**Note:** The Titan benchmarks are not included with the VTR release (due to their size). However they can be downloaded and extracted by running make get\_titan\_benchmarks from the root of the VTR tree. They can also be downloaded manually.

#### See also:

Running the Titan Benchmarks

# 2.5.3 MCNC20 Benchmarks

The MCNC benchmarks [Yan91] are a set of small and old (circa 1991) benchmarks. They consist primarily of logic (i.e. LUTs) with few registers and no hard blocks.

**Warning:** The MCNC20 benchmarks are not recommended for modern FPGA CAD and architecture research. Their small size and design style (e.g. few registers, no hard blocks) make them unrepresentative of modern FPGA usage. This can lead to misleading CAD and/or architecture conclusions.

The MCNC20 benchmarks included with VTR are available as .blif files under:

```

$VTR_ROOT/vtr_flow/benchmarks/blif/

```

The versions used in the VPR 4.3 release, which were mapped to *K*-input look-up tables using FlowMap [CD94], are available under:

\$VTR\_ROOT/vtr\_flow/benchmarks/blif/<#>

where  $K = \langle \# \rangle$ .

| Benchmark | Approximate Number of Netlist Primitives |

|-----------|------------------------------------------|

| alu4      | 934                                      |

| apex2     | 1116                                     |

| apex4     | 916                                      |

| bigkey    | 1561                                     |

| clma      | 3754                                     |

| des       | 1199                                     |

| diffeq    | 1410                                     |

| dsip      | 1559                                     |

| elliptic  | 3535                                     |

| ex1010    | 2669                                     |

| ex5p      | 824                                      |

| frisc     | 3291                                     |

| misex3    | 842                                      |

| pdc       | 2879                                     |

| s298      | 732                                      |

| s38417    | 4888                                     |

| s38584.1  | 4726                                     |

| seq       | 1041                                     |

| spla      | 2278                                     |

| tseng     | 1583                                     |

#### Table 2.2: The MCNC20 benchmarks.

# 2.6 Power Estimation

VTR provides transistor-level dynamic and static power estimates for a given architecture and circuit.

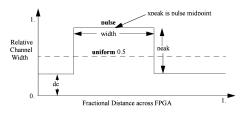

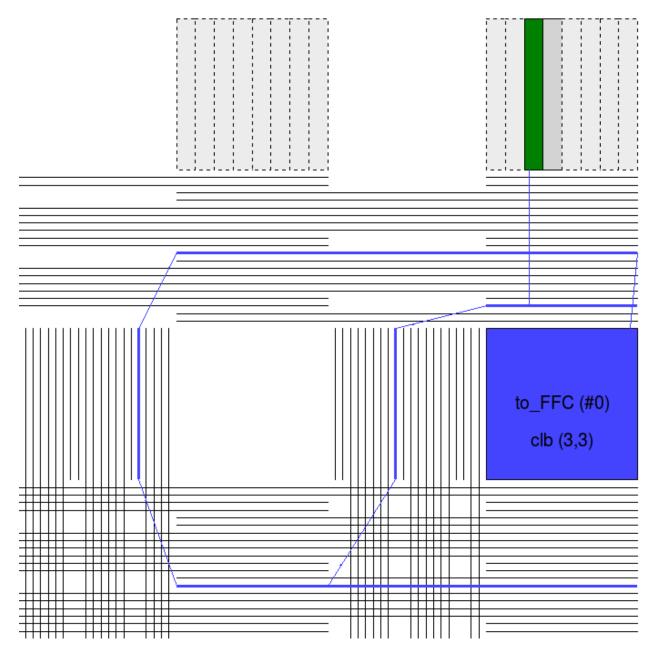

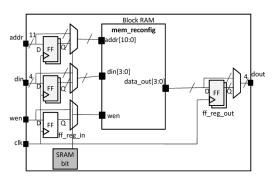

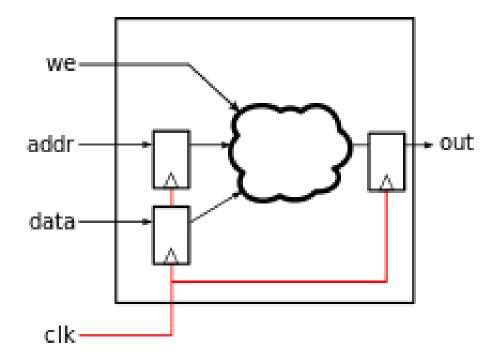

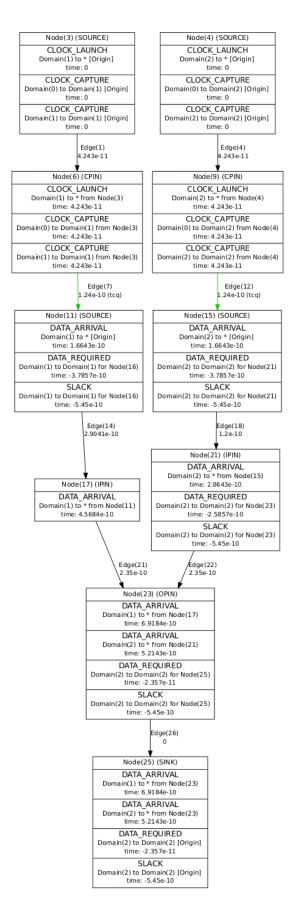

Fig. 2.2 illustrates how power estimation is performed in the VTR flow. The actual power estimation is performed within the *VPR* executable; however, additional files must be provided. In addition to the circuit and architecture files, power estimation requires files detailing the signal activities and technology properties.

*Running VTR with Power Estimation* details how to run power estimation for VTR. *Supporting Tools* provides details on the supporting tools that are used to generate the signal activities and technology properties files. *Architecture Modelling* provides details about how the tool models architectures, including different modelling methods and options. *Other Architecture Options & Techniques* provides more advanced configuration options.

# 2.6.1 Running VTR with Power Estimation

#### **VTR Flow**

The easiest way to run the VTR flow is to use the *run\_vtr\_flow* script.

In order to perform power estimation, you must add the following options:

- run\_vtr\_flow.pl -power

- run\_vtr\_flow.pl -cmos\_tech <cmos\_tech\_properties\_file>

The CMOS technology properties file is an XML file that contains relevant process-dependent information needed for power estimation. XML files for 22nm, 45nm, and 130nm PTM models can be found here:

\$VTR\_ROOT/vtrflow/tech/\*

See Technology Properties for information on how to generate an XML file for your own SPICE technology model.

#### VPR

Power estimation can also be run directly from VPR with the following (all required) options:

- *vpr* --*power*: Enables power estimation.

- vpr --activity\_file <activities.act>: The activity file, produce by ACE 2.0, or another tool.

- vpr --tech\_properties <tech\_properties.xml>: The technology properties file.

Power estimation requires an activity file, which can be generated as described in ACE 2.0 Activity Estimation.

# 2.6.2 Supporting Tools

#### **Technology Properties**

Power estimation requires information detailing the properties of the CMOS technology. This information, which includes transistor capacitances, leakage currents, etc. is included in an .xml file, and provided as a parameter to VPR. This XML file is generated using a script which automatically runs HSPICE, performs multiple circuit simulations, and extract the necessary values.

Some of these technology XML files are included with the release, and are located here:

Fig. 2.2: Power Estimation in the VTR Flow

\$VTR\_ROOT/vtr\_flow/tech/\*

If the user wishes to use a different CMOS technology file, they must run the following script:

**Note:** HSPICE must be available on the users path

where:

- <tech\_file>: Is a SPICE technology file, containing a pmos and nmos models.

- <tech\_size>: The technology size, in meters.

#### **Example:**

A 90nm technology would have the value 90e-9.

- <vdd>: Supply voltage in Volts.

- <temp>: Operating temperature, in Celcius.

#### ACE 2.0 Activity Estimation

Power estimation requires activity information for the entire netlist. This ativity information consists of two values:

1. The Signal Probability,  $P_1$ , is the long-term probability that a signal is logic-high.

#### **Example:**

A clock signal with a 50% duty cycle will have  $P_1(clk) = 0.5$ .

2. The Transition Density (or switching activity),  $A_S$ , is the average number of times the signal will switch during each clock cycle.

**Example:**

A clock has  $A_S(clk) = 2$ .

The default tool used to perform activity estimation in VTR is ACE 2.0 [LW06]. This tool was originally designed to work with the (now obsolete) Berkeley SIS tool ACE 2.0 was modifed to use ABC, and is included in the VTR package here:

\$VTR\_ROOT/ace2

The tool can be run using the following command-line arguments:

\$VTR\_ROOT/ace2/ace -b <abc.blif> -c <clock\_name> -o <activities.act> -n <new.blif>

where

- <abc.blif>: Is the input BLIF file produced by ABC.

- <clock\_name>: Is the name of the clock in the input BLIF file

- <activities.act>: Is the activity file to be created.

- <new.blif>: The new BLIF file.

This will be functionally identical in function to the ABC blif; however, since ABC does not maintain internal node names, a new BLIF must be produced with node names that match the activity file.

User's may with to use their own activity estimation tool. The produced activity file must contain one line for each net in the BLIF file, in the following format:

<net name> <signal probability> <transistion density>

### 2.6.3 Architecture Modelling

The following section describes the architectural assumptions made by the power model, and the related parameters in the architecture file.

#### **Complex Blocks**

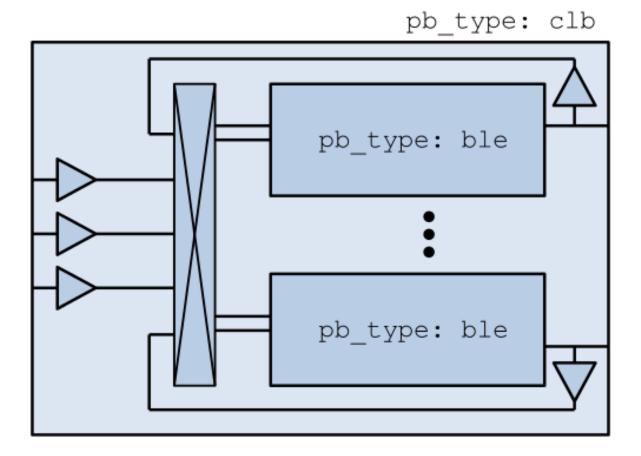

The VTR architecture description language supports a hierarchichal description of blocks. In the architecture file, each block is described as a pb\_type, which may includes one or more children of type pb\_type, and interconnect structures to connect them.

The power estimation algorithm traverses this hierarchy recursively, and performs power estimation for each pb\_type. The power model supports multiple power estimation methods, and the user specifies the desired method in the architecture file:

```

<pb_type>

<power method="<estimation-method>"/>

</pb_type>

```

The following is a list of valid estimation methods. Detailed descriptions of each type are provided in the following sections. The methods are listed in order from most accurate to least accurate.

1. specify-size: Detailed transistor level modelleling.

The user supplies all buffer sizes and wire-lengths. Any not provided by the user are ignored.

2. auto-size: Detailed transistor level modelleling.

The user can supply buffer sizes and wire-lengths; however, they will be automatically inserted when not provided.

3. pin-toggle: Higher-level modelling.

The user specifies energy per toggle of the pins. Static power provided as an absolute.

4. C-internal: Higher-level modelling.

The user supplies the internal capacitance of the block. Static power provided as an absolute.

5. absolute: Highest-level modelling.

The user supplies both dynamic and static power as absolutes.

Other methods of estimation:

- 1. ignore: The power of the pb\_type is ignored, including any children.

- 2. sum-of-children: Power of pb\_type is solely the sum of all children pb\_types.

Interconnect between the pb\_type and its children is ignored.

**Note:** If no estimation method is provided, it is inherited from the parent pb\_type.

Note: If the top-level pb\_type has no estimation method, auto-size is assumed.

#### specify-size

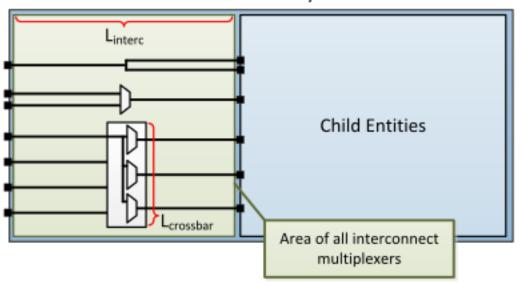

This estimation method provides a detailed transistor level modelling of CLBs, and will provide the most accurate power estimations. For each  $pb_type$ , power estimation accounts for the following components (see Fig. 2.3).

- Interconnect multiplexers

- Buffers and wire capacitances

- Child pb\_types

#### Fig. 2.3: Sample Block

**Multiplexers:** Interconnect multiplexers are modelled as 2-level pass-transistor multiplexers, comprised of minimumsize NMOS transistors. Their size is determined automatically from the <interconnect/> structures in the architecture description file. **Buffers and Wires:** Buffers and wire capacitances are not defined in the architecture file, and must be explicitly added by the user. They are assigned on a per port basis using the following construct:

```

<pb_type>

<input name="my_input" num_pins="1">

<power ...options.../>

</input>

</pb_type>

```

The wire and buffer attributes can be set using the following options. If no options are set, it is assumed that the wire capacitance is zero, and there are no buffers present. Keep in mind that the port construct allows for multiple pins per port. These attributes will be applied to each pin in the port. If necessary, the user can seperate a port into multiple ports with different wire/buffer properties.

- wire\_capacitance=1.0e-15: The absolute capacitance of the wire, in Farads.

- wire\_length=1.0e-7: The absolute length of the wire, in meters.

The local interconnect capacitance option must be specified, as described in *Local Interconnect Capacitance*.

- wire\_length=auto: The wirelength is automatically sized. See Local Wire Auto-Sizing.

- buffer\_size=2.0: The size of the buffer at this pin. See for more *Buffer Sizing* information.

- buffer\_size=auto: The size of the buffer is automatically sized, assuming it drives the above wire capacitance and a single multiplexer. See *Buffer Sizing* for more information.

**Primitives:** For all child pb\_types, the algorithm performs a recursive call. Eventually pb\_types will be reached that have no children. These are primitives, such as flip-flops, LUTs, or other hard-blocks. The power model includes functions to perform transistor-level power estimation for flip-flops and LUTs. If the user wishes to use a design with other primitive types (memories, multipliers, etc), they must provide an equivalent function. If the user makes such a function, the power\_calc\_primitive function should be modified to call it. Alternatively, these blocks can be configured to use higher-level power estimation methods.

### auto-size

This estimation method also performs detailed transistor-level modelling. It is almost identical to the specify-size method described above. The only difference is that the local wire capacitance and buffers are automatically inserted for all pins, when necessary. This is equivalent to using the specify-size method with the wire\_length=auto and buffer\_size=auto options for every port.

### Note: This is the default power estimation method.

Although not as accurate as user-provided buffer and wire sizes, it is capable of automatically capturing trends in power dissipation as architectures are modified.

### pin-toggle

This method allows users to specify the dynamic power of a block in terms of the energy per toggle (in Joules) of each input, output or clock pin for the pb\_type. The static power is provided as an absolute (in Watts). This is done using the following construct:

Keep in mind that the port construct allows for multiple pins per port. Unless an subset index is provided, the energy per toggle will be applied to each pin in the port. The energy per toggle can be scaled by another signal using the scaled\_by\_static\_prob. For example, you could scale the energy of a memory block by the read enable pin. If the read enable were high 80% of the time, then the energy would be scaled by the *signal\_probability*, 0.8. Alternatively scaled\_by\_static\_prob\_n can be used for active low signals, and the energy will be scaled by  $(1 - signal_probability)$ .

This method does not perform any transistor-level estimations; the entire power estimation is performed using the above values. It is assumed that the power usage specified here includes power of all child pb\_types. No further recursive power estimation will be performed.

### C-internal

This method allows the users to specify the dynamic power of a block in terms of the internal capacitance of the block. The activity will be averaged across all of the input pins, and will be supplied with the internal capacitance to the standard equation:

$$P_{dyn} = \frac{1}{2}\alpha CV^2.$$

Again, the static power is provided as an absolute (in Watts). This is done using the following construct:

It is assumed that the power usage specified here includes power of all child pb\_types. No further recursive power estimation will be performed.

### absolute

This method is the most basic power estimation method, and allows users to specify both the dynamic and static power of a block as absolute values (in Watts). This is done using the following construct:

It is assumed that the power usage specified here includes power of all child pb\_types. No further recursive power estimation will be performed.

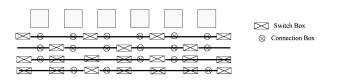

# 2.6.4 Global Routing

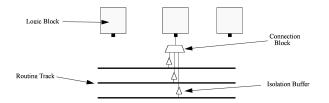

Global routing consists of switch boxes and input connection boxes.

### **Switch Boxes**

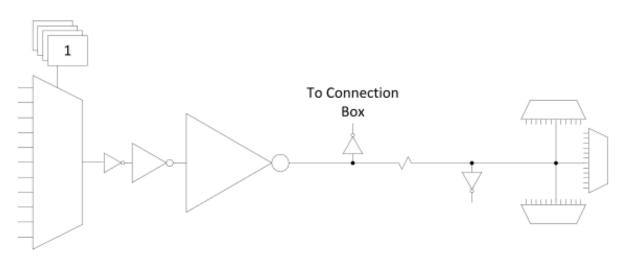

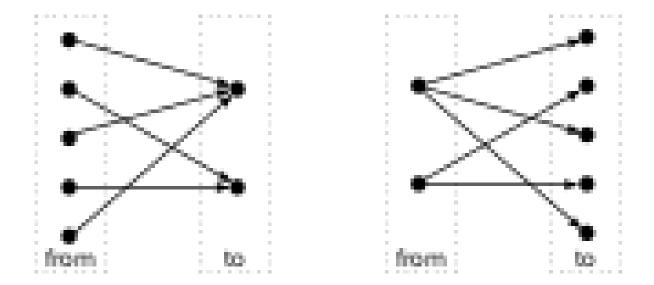

Switch boxes are modelled as the following components (Fig. 2.4):

- 1. Multiplexer

- 2. Buffer

- 3. Wire capacitance

### Fig. 2.4: Switch Box

**Multiplexer:** The multiplexer is modelled as 2-level pass-transistor multiplexer, comprised of minimum-size NMOS transistors. The number of inputs to the multiplexer is automatically determined.

**Buffer:** The buffer is a multistage CMOS buffer. The buffer size is determined based upon output capacitance provided in the architecture file:

```

<switchlist>

<switch type="mux" ... C_out="1.0e-16"/>

</switchlist>

```

The user may override this method by providing the buffer size as shown below:

```

<switchlist>

<switch type="mux" ... power_buf_size="16"/>

</switchlist>

```

The size is the drive strength of the buffer, relative to a minimum-sized inverter.

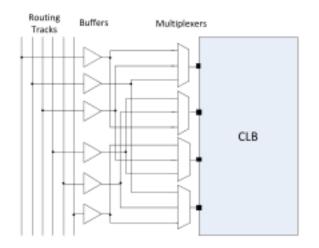

### **Input Connection Boxes**

Input connection boxes are modelled as the following components (Fig. 2.5):

- One buffer per routing track, sized to drive the load of all input multiplexers to which the buffer is connected (For buffer sizing see *Buffer Sizing*).

- One multiplexer per block input pin, sized according to the number of routing tracks that connect to the pin.

Fig. 2.5: Connection Box

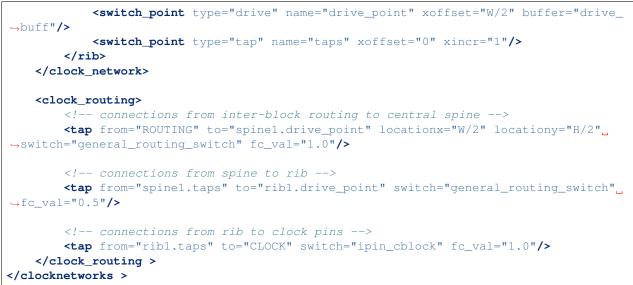

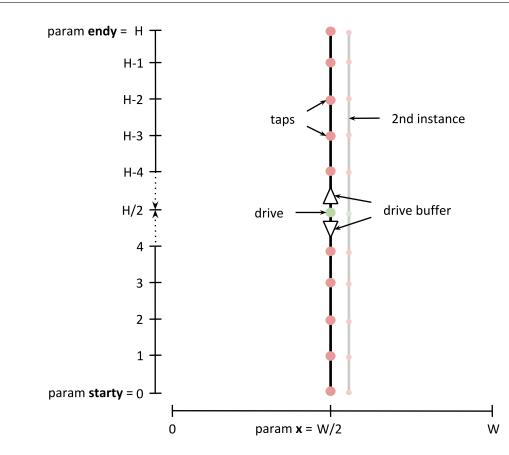

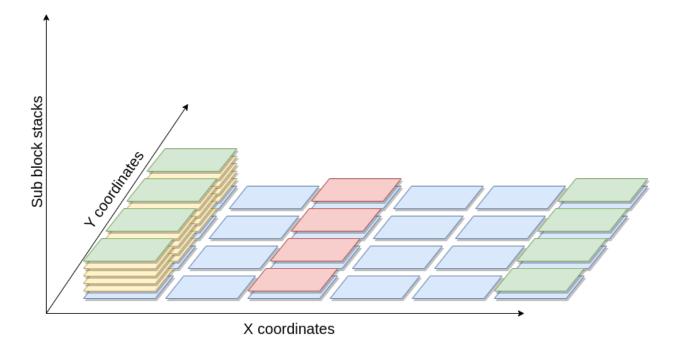

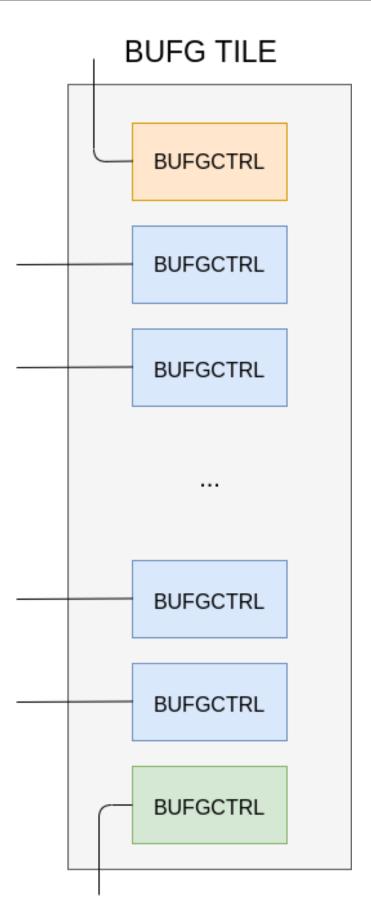

### **Clock Network**

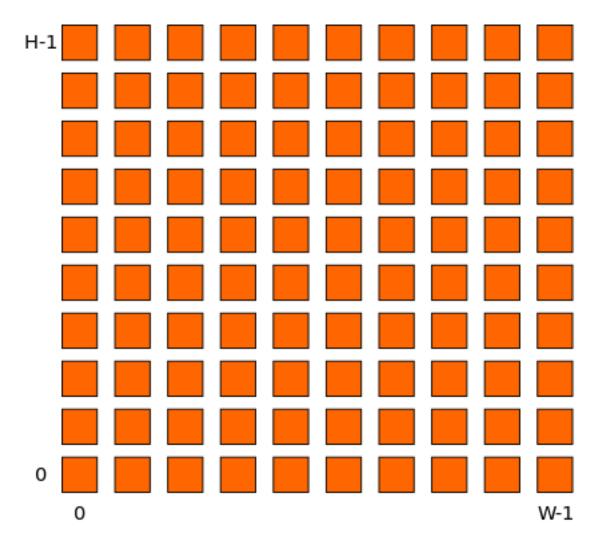

The clock network modelled is a four quadrant spine and rib design, as illustrated in Fig. 2.6. At this time, the power model only supports a single clock. The model assumes that the entire spine and rib clock network will contain buffers separated in distance by the length of a grid tile. The buffer sizes and wire capacitances are specified in the architecture file using the following construct:

```

<clocks>

<clock ... clock_options ... />

</clocks>

```

The following clock options are supported:

- C\_wire=1e-16: The absolute capacitance, in fards, of the wire between each clock buffer.

- C\_wire\_per\_m=1e-12: The wire capacitance, in fards per m.

The capacitance is calculated using an automatically determined wirelength, based on the area of a tile in the FPGA.

• buffer\_size=2.0: The size of each clock buffer.

This can be replaced with the auto keyword. See *Buffer Sizing* for more information on buffer sizing.

Fig. 2.6: The clock network. Squares represent CLBs, and the wires represent the clock network.

# 2.6.5 Other Architecture Options & Techniques

### Local Wire Auto-Sizing

Due to the significant user effort required to provide local buffer and wire sizes, we developed an algorithm to estimate them automatically. This algorithm recursively calculates the area of all entities within a CLB, which consists of the area of primitives and the area of local interconnect multiplexers. If an architecture uses new primitives in CLBs, it should include a function that returns the transistor count. This function should be called from within power\_count\_transistors\_primitive().

In order to determine the wire length that connects a parent entity to its children, the following assumptions are made:

- Assumption 1: All components (CLB entities, multiplexers, crossbars) are assumed to be contained in a squareshaped area.

- Assumption 2: All wires connecting a parent entity to its child pass through the *interconnect square*, which is the sum area of all interconnect multiplexers belonging to the parent entity.

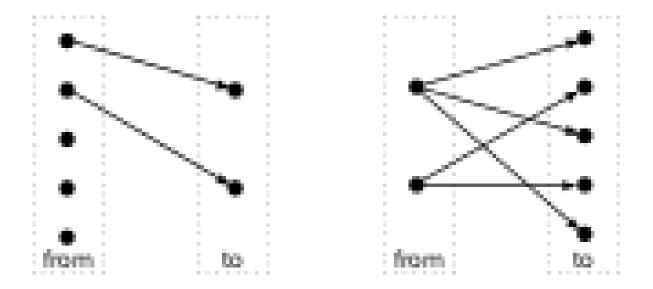

Fig. 2.7 provides an illustration of a parent entity connected to its child entities, containing one of each interconnect type (direct, many-to-1, and complete). In this figure, the square on the left represents the area used by the transistors of the interconnect multiplexers. It is assumed that all connections from parent to child will pass through this area. Real wire lengths could me more or less than this estimate; some pins in the parent may be directly adjacent to child entities, or they may have to traverse a distance greater than just the interconnect area. Unfortuantely, a more rigorous estimation would require some information about the transistor layout.

Parent Entity

Fig. 2.7: Local interconnect wirelength.

| Table 2.3: Local interconnect wirelength and capacitance. | $C_{inv}$ is the |

|-----------------------------------------------------------|------------------|

| input capacitance of a minimum-sized inverter.            |                  |

| Connection from Entity Pin to:        | Estimated Wirelength                  | Transistor Capacitance |

|---------------------------------------|---------------------------------------|------------------------|

| Direct (Input or Output)              | $0.5 \cdot L_{interc}$                | 0                      |

| Many-to-1 (Input or Output)           | $0.5 \cdot L_{interc}$                | $C_{INV}$              |

| Complete <i>m</i> : <i>n</i> (Input)  | $0.5 \cdot L_{interc} + L_{crossbar}$ | $n \cdot C_{INV}$      |

| Complete <i>m</i> : <i>n</i> (Output) | $0.5 \cdot L_{interc}$                | $C_{INV}$              |

Table 2.3 details how local wire lengths are determined as a function of entity and interconnect areas. It is assumed that each wire connecting a pin of a pb\_type to an interconnect structure is of length  $0.5 \cdot L_{interc}$ . In reality, this length depends on the actual transistor layout, and may be much larger or much smaller than the estimated value. If desired, the user can override the 0.5 constant in the architecture file:

```

<architecture>

<power>

<local_interconnect factor="0.5"/>

</power>

</architecture>

```

### **Buffer Sizing**

In the power estimator, a buffer size refers to the size of the final stage of multi-stage buffer (if small, only a single stage is used). The specified size is the  $\frac{W}{L}$  of the NMOS transistor. The PMOS transistor will automatically be sized larger. Generally, buffers are sized depending on the load capacitance, using the following equation:

Buffer Size =

$$\frac{1}{2 \cdot f_{LE}} * \frac{C_{Load}}{C_{INV}}$$

In this equation,  $C_{INV}$  is the input capacitance of a minimum-sized inverter, and  $f_{LE}$  is the logical effort factor. The logical effort factor is the gain between stages of the multi-stage buffer, which by default is 4 (minimal delay). The term  $(2 \cdot f_{LE})$  is used so that the ratio of the final stage to the driven capacitance is smaller. This produces a much lower-area, lower-power buffer that is still close to the optimal delay, more representative of common design practises. The logical effort factor can be modified in the architecture file:

```

<architecture>

<power>

<buffers logical_effor_factor="4"/>

</power>

</architecture>

```

### Local Interconnect Capacitance

If using the auto-size or wire-length options (*Architecture Modelling*), the local interconnect capacitance must be specified. This is specified in the units of Farads/meter.

```

<architecture>

<power>

<local_interconnect C_wire="2.5e-15"/>

</power>

</architecture>

```

# 2.7 Tasks

Tasks provide a framework for running the VTR flow on multiple benchmarks, architectures and with multiple CAD tool parameters.

A task specifies a set of benchmark circuits, architectures and CAD tool parameters to be used. By default, tasks execute the *run\_vtr\_flow* script for every circuit/architecture/CAD parameter combination.

# 2.7.1 Example Tasks

- basic\_flow: Runs the VTR flow mapping a simple Verilog circuit to an FPGA architecture.

- timing: Runs the flagship VTR benchmarks on a comprehensive, realistic architecture file.

- timing\_chain: Same as timing but with carry chains.

- regression\_mcnc: Runs VTR on the historical MCNC benchmarks on a legacy architecture file. (Note: This is only useful for comparing to the past, it is not realistic in the modern world)

- regression\_titan/titan\_small: Runs a small subset of the Titan benchmarks targetting a simplified Altera Stratix IV (commercial FPGA) architecture capture

- regression\_fpu\_hard\_block\_arch: Custom hard FPU logic block architecture

# 2.7.2 Directory Layout

All of VTR's included tasks are located here:

\$VTR\_ROOT/vtr\_flow/tasks

If users wishes to create their own task, they must do so in this location.

All tasks must contain a configuration file located here:

\$VTR\_ROOT/vtr\_flow/tasks/<task\_name>/config/config.txt

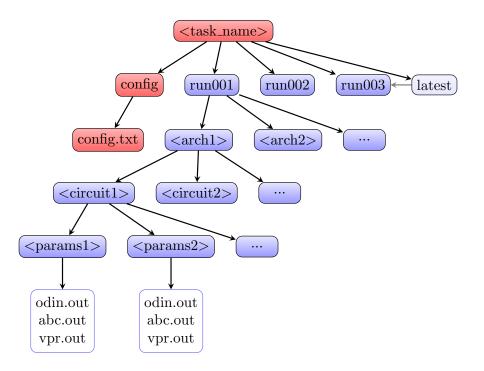

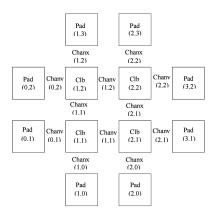

Fig. 2.8 illustrates the directory layout for a VTR task. Every time the task is run a new run < # > directory is created to store the output files, where < # > is the smallest integer to make the run directory name unique.

The symbolic link latest will point to the most recent run<#> directory.

Fig. 2.8: Task directory layout.

# 2.7.3 Creating a New Task

- 1. Create the folder \$VTR\_ROOT/vtr\_flow/tasks/<task\_name>

- 2. Create the folder \$VTR\_ROOT/vtr\_flow/tasks/<task\_name>/config

- 3. Create and configure the file \$VTR\_ROOT/vtr\_flow/tasks/<task\_name>/config/config.txt

# 2.7.4 Task Configuration File

The task configuration file contains key/value pairs separated by the = character. Comment line are indicted using the # symbol.

Example configuration file:

```

# Path to directory of circuits to use

circuits_dir=benchmarks/verilog

# Path to directory of architectures to use

archs_dir=arch/timing

# Add circuits to list to sweep

circuit_list_add=ch_intrinsics.v

circuit_list_add=diffeq1.v

# Add architectures to list to sweep

arch_list_add=k6_N10_memSize16384_memData64_stratix4_based_timing_sparse.xml

# Parse info and how to parse

parse_file=vpr_standard.txt

```

**Note:** *run\_vtr\_task* will invoke the script (default *run\_vtr\_flow*) for the cartesian product of circuits, architectures and script parameters specified in the config file.

# 2.7.5 Required Fields

• circuit\_dir: Directory path of the benchmark circuits.

Absolute path or relative to \$VTR\_ROOT/vtr\_flow/.

• arch\_dir: Directory path of the architecture XML files.

Absolute path or relative to \$VTR\_ROOT/vtr\_flow/.

• circuit\_list\_add: Name of a benchmark circuit file.

Use multiple lines to add multiple circuits.

• arch\_list\_add: Name of an architecture XML file.

Use multiple lines to add multiple architectures.

• parse\_file: Parse Configuration file used for parsing and extracting the statistics.

Absolute path or relative to \$VTR\_ROOT/vtr\_flow/parse/parse\_config.

# 2.7.6 Optional Fields

• script\_path: Script to run for each architecture/circuit combination.

Absolute path or relative to \$VTR\_ROOT/vtr\_flow/scripts/or \$VTR\_ROOT/vtr\_flow/tasks/<task\_name>/config/)

**Default:** run\_vtr\_flow

Users can set this option to use their own script instead of the default. The circuit path will be provided as the first argument, and architecture path as the second argument to the user script.

• script\_params\_common: Common parameters to be passed to all script invocations.

This can be used, for example, to run partial VTR flows.

Default: none

- script\_params: Alias for script\_params\_common

- script\_params\_list\_add: Adds a set of command-line arguments

Multiple *script\_params\_list\_add* can be provided which are addded to the cartesian product of configurations to be evaluated.

• sdc\_dir: Directory path to benchmark SDC files.

Absolute path or relative to \$VTR\_ROOT/vtr\_flow/.

If provided, each benchmark will look for a similarly named SDC file.

For instance with circuit\_list\_add=my\_circuit.v or circuit\_list\_add=my\_circuit.blif, the flow would look for an SDC file named my\_circuit.sdc within the specified sdc\_dir.

• pass\_requirements\_file: Pass Requirements file.

Absolute path or relative to \$VTR\_ROOT/vtr\_flow/parse/pass\_requirements/ or \$VTR\_ROOT/vtr\_flow/tasks/<task\_name>/config/

Default: none

# 2.8 run\_vtr\_flow

This script runs the VTR flow for a single benchmark circuit and architecture file.

The script is located at:

\$VTR\_ROOT/vtr\_flow/scripts/run\_vtr\_flow.pl

# 2.8.1 Basic Usage

At a minimum run\_vtr\_flow.pl requires two command-line arguments:

run\_vtr\_flow.pl <circuit\_file> <architecture\_file>

where:

- <circuit\_file> is the circuit to be processed

- <architecture\_file> is the target FPGA architecture

Note: The script will create a ./temp directory, unless otherwise specified with the  $-temp\_dir$  option. The circuit file and architecture file will be copied to the temporary directory. All stages of the flow will be run within this directory. Several intermediate files will be generated and deleted upon completion. Users should ensure that no important files are kept in this directory as they may be deleted.

# 2.8.2 Output

The standard out of the script will produce a single line with the format:

```

<architecture>/<circuit_name>...<status>

```

If execution completed successfully the status will be 'OK'. Otherwise, the status will indicate which stage of execution failed.

The script will also produce an output files (\*.out) for each stage, containing the standout output of the executable(s).

# 2.8.3 Advanced Usage

Additional optional command arguments can also be passed to run\_vtr\_flow.pl:

run\_vtr\_flow.pl <circuit\_file> <architecture\_file> [<options>] [<vpr\_options>]

where:

- <options> are additional arguments passed to run\_vtr\_flow.pl (described below),

- <vpr\_options> are any arguments not recognized by run\_vtr\_flow.pl. These will be forwarded to VPR.

For example:

run\_vtr\_flow.pl my\_circuit.v my\_arch.xml -track\_memory\_usage --pack --place

will run the VTR flow to map the circuit my\_circuit.v onto the architecture my\_arch.xml; the arguments --pack and --place will be passed to VPR (since they are unrecognized arguments to run\_vtr\_flow.pl). They will cause VPR to perform only *packing and placement*.

# 2.8.4 Detailed Command-line Options

Note: Any options not recognized by this script is forwarded to VPR.

```

-starting_stage <stage>

```

Start the VTR flow at the specified stage.

Accepted values:

- odin

- abc